制造商:Silvaco中国

Gateway支持任何技术的平展式或分层次设计。Gateway通过EDIF200标准文件格式,接受其它原理图编辑器(PSPICE, OrCAD, Composer等) 的原有设计。Gateway可经由全局参数设定,以不同的特别工作空间

(workplace)处理多种设计和技术。

Gateway特征:

• 强大的电路图捕捉和编辑功能,可创建和修改多视窗、多图表和分层次IC设计

• GatewayViews需许可以检视和导航原理图设计,许可证免费

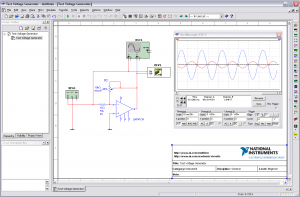

• 与SmartSpice电路图仿真器的无缝集成,创造一个配合行为模型,交互探测、波形显示和分析的交互式

设计环境

• 创建HSPICE兼容的输入deck档

• 以共享工作空间管理多用户项目,可共享设计团队所使用的单元库和符号库

• 可通过EDIF200,将其他原理图捕捉工具平滑过渡至Gateway

• 从原理图产生网表,用于仿真、基于网表的版图(NDL)和LVS

• Silvaco强大的加密功能可以用来保护客户和第三方的知识产权

全功能性:

• 易于创建符号、子电路、子电路图和Verilog-A模型

• 对仿真、电路图驱使的版图和LVS兼容性提供完备的符号创建

• 用户可配置键,用于执行重复的任务,并效仿既有的捕捉工具

• 全面的搜索和替换功能来处理参数编辑、IP复用和交互式设计

• 对模块化、可重复使用的设计和库作分层次捕捉,并可同时用于原有电路

• 强大的现场编辑功能可用于布线、总线、拆总线和混总线

• 设计师可设置检查规则,以显示电路绘制规则违例和非法命名

• 参数化单元 (Pcells) 经由源设计输入数据的设置可 自动生成“设计-规则-连接”版图组件

易用性:

• 具有直观的从左到右的设计方法、工具提示和批处理仿真控制的功能,无论对新设计师还是经验丰富的设计师,都简单易用

• 对设置带有库文件的多用户环境及使用EDIF导入原有数据都相当容易

• 新用户可参照帮助功能和工具提示

• 批处理仿真选项可直接从原理图中调用

• 参数最小值/更大值检查可排除输入错误

• 支持线到线, 线到引脚, 按线名, 和隐式/全局连接

集成定制IC设计平台

• 用于全定制模拟电路的前端至后端(Front-to-back)全自动设计解决方案

• 以验证的反馈流程连接Simucad行为模型、电路图、电路仿真版图、DRC、LVS和寄生提取

• 与SmartView的图形化波形后处理器集成,以矢量计算完成延迟、斜率、过冲、上升时间和眼图的重叠计算

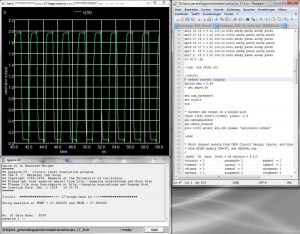

• 原理图和后处理之间强大的交互探测提供了实时的设计反馈

• 对设计规则、偏差、参数计算和工艺斜度等做实时地回调计算

• 显示整个分层次设计中的直流偏流与偏压

设计高效

• 以多视窗方式显示版图、仿真和LVS,以提供设计完整性和流畅的投片(tapeout)

• 数据表数据输入、网表导入、EDIF读数装置和自动的符号生成等使重复使用既有电路更方便

• 支持设计工具包中符号背后的加密网表以便于IP分布

• 行进式波形允许实时地查看仿真结果以检查长时间仿真

• 有效控制电路图、仿真和分析之间的设计流程

• 醒目标出误差,放大在原理图上的位置/级别,以便于修改