制造商:ANSYS, Inc.

ANSYS PathFinder是一款面向全芯片SoC和IP设计的静电放电(ESD)规划、验证和签核解决方案。工程师可进行布局分析和电路级分析以识别并隔离设计问题,从而防止芯片或IP因带电器件模型(CDM)、人体模型(HBM)和其它ESD事件出现故障。此外,由于该技术能够执行精确的互联寄生抽取、ESD仿真和电迁移(EM)以及电流密度规则处理等功能,很多代工厂都对它进行了认证。

使用全芯片级建模技术,ANSYS PathFinder能判断设计是否满足ESD指南,还能确定设计(布局或电路)中最薄弱的环节。该软件能够执行早期原型构建和设计探索。PathFinder 能为ESD事件建模,分析设计并预测钳位单元是否有效。

软件的功能介绍:

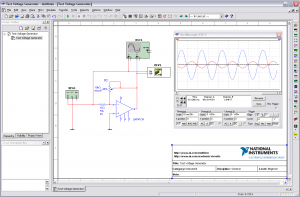

集成型单次仿真与结果分析

PathFinder可在统一的工具环境中实现优化的单次通过模型,有助于读入设计数据,设置ESD规则,执行抽取和ESD仿真,分析根源,并提供修复和优化反馈。该软件使用行业标准数据格式,例如GDS和DEF。在指定已选中的各种规则和相关参数方面,该软件具有相当大的灵活性,使设计人员能够实施广泛的验证。

全芯片功能

PathFinder可对具有一亿以上例化的超大型SOC设计执行ESD完整性检查。它能处理数百个电源/接地/信号网络,并在单次仿真中执行电阻和电流密度仿真。根据尺寸、金属层数量、PG网络复杂性、电源/接地/信号网络数量以及ESD器件数量的不同,全芯片ESD仿真需要几小时至一天的周转时间。此外,PathFinder还包含多线程和分布式计算选项,可用于处理超大型设计。

基于版图的分析与根源识别

作为一款基于版图的ESD分析与验收解决方案,ANSYS PathFinder能识别可导致ESD事件诱发故障的版图问题和连接失衡问题。通过穿越芯片内任意两个相关点之间的每条传导路径,PathFinder能够验证连接稳健性,并根据代工厂或用户规定的限制检查电气特性。利用芯片设计数据库、代工厂指定技术参数和ESD验收限制,软件能够快速、精确地计算所要求的电气参数,并依照指定限制进行验证。PathFinder提供多种基于GUI的调试功能,可帮助设计人员快速识别版图问题并在提交修复之前执行假设分析。用户可生成“通过-失败”报告,用于在GUI中交叉探测版图情况。

全面覆盖

PathFinder的ESD分析、验证和验收功能覆盖从初始设计阶段到流片的整个过程。在版图规划阶段,设计人员可通过优化内核钳位版图和执行假设分析来进行权衡分析。这样他们就可有效地规划资源。PathFinder通过读入IP或I/O级版图数据,可执行基于版图的验收检查,从而实现对I/O焊盘和钳位版图布局的优化。对于IP而言,用户可以使用PathFinder来执行瞬态ESD仿真,以便更好地掌握ESD放电路径并识别受应力的器件接点。为识别I/O和/或IP集成过程中产生的薄弱环节,可生成嵌入式ESD器件模型的ESD宏模型,并在全芯片级ESD验收检查中实现无缝应用。

HBM/MM ESD Events

ANSYS PathFinder让zap电流通过电源/接地网络,用以模拟ESD放电过程中的HBM/MM ESD事件,从而鉴别版图中的瓶颈。软件可对任意焊盘注入的电流以及后续流过芯片上互连线的电流进行建模,以识别不能有效处理ESD事件中出现的高电流的引脚-钳位-引脚路径。软件能估计连接焊盘的线路中的电流密度,并根据代工厂指定的限制进行检查,突出显示出多种问题,例如钳位/二极管引脚上的失衡连接,以及尺寸不足的过孔或者ESD放电路径中过窄的金属段。与基于DRC的检查不同,PathFinder的互联线路故障分析功能可实现一种能覆盖ESD放电路径中每个可能线路段/过孔的综合方法。

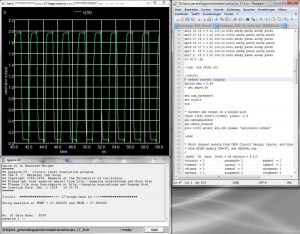

SPICE相关的精度

PathFinder可提供精确的瞬态仿真,并可对晶片衬底以及复杂ESD器件的骤回行为进行建模。在IP层面,该软件能抽取电源/接地和衬底RC网络,并执行瞬态仿真。它可针对功能器件和寄生器件(例如量子阱二极管)引入SPICE模型,并精确执行皮秒级的瞬态仿真,并获得SPICE相关结果。具有骤回行为的钳位通常在SPICE中存在收敛问题;PathFinder的仿真引擎经过专门定制,适用于处理钳位器件的骤回行为,从而可精确建模ESD器件触发,并识别ESD事件中受应力的器件接点。