制造商:Silvaco中国

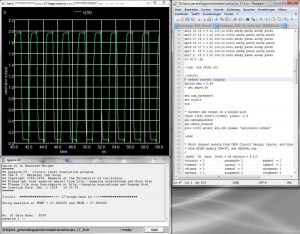

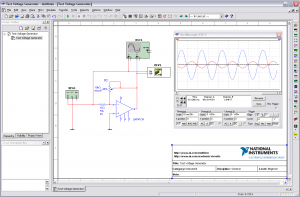

ClarityRLC是一个高效而精准的工具,用于约简所提取的电路连线表中的线性寄生RLC元件。ClarityRLC是基于

散射参数基宏建模法(Scattering-Parameter-Based Macromodeling)和时域法(Time Domain)。

特征:

• 可处理由常见EDA寄生提取器所生成的上百万个寄生元件的电路网表

• 可显著缩短后版图和后布线仿真的运行时间

• 可过滤悬空元件,以及小于用户所定义的阈值的元件

• 可进行串联合并和并联合并

• 使用基于散射参数的宏建模法进行线性时间的电路网表约简,并依据连线表的约简指数,在宏建模法与时域法之间进行切换

• 除可分析电容电阻树(RC-tress)之外,还可分析其他互连模型。因此,Clarity RLC可处理耦合电容和电阻回路,而不失其一般性。

• 支持SPICE、DSPF或SPEF格式

• Silvaco强大的加密功能可以用来保护客户和第三方的知识产权

约简高效,简便易用:

• 与原始网络的SPICE仿真结果相比,误差小于 3%。

• 可约简RLC网络中高达95%的寄生元件

• 使用LISA定制脚本语言,处理子电路、单元和网络的选择

• 可生成全面的约简过程报告

• 可在 Linux (64 bit)和Windows 平台上使用

© 版权声明

文章版权归作者所有,未经允许请勿转载。

THE END